# Uma Investigação Sobre a Robustez e Figuras de Mérito de Portas Lógicas em Pontos Quânticos de Silício em uma Biblioteca Proposta

Hilário Corrêa da Silva Neto

Dep. de Ciência da Computação

Universidade Federal de Minas Gerais

Belo Horizonte, Brasil

hilariocorrean@dcc.ufmg.br

Omar Paranaíba Vilela Neto

Dep. de Ciência da Computação

Universidade Federal de Minas Gerais

Belo Horizonte, Brasil

omar@dcc.ufmg.br

João Gabriel de Oliveira Bicalho

Dep. de Ciência da Computação

Universidade Federal de Minas Gerais

Belo Horizonte, Brasil

joao.bicalho@dcc.ufmg.br

**Abstract**—Conforme se atingem os limites físicos da implementação de circuitos lógicos baseados em CMOS, faz-se urgente a busca por novos paradigmas de tecnologias que complementem ou substituam o estado atual. Dentre estas alternativas, a nanocomputação por acoplamento de campo (FCN) se mostra promissora, e uma das implementações possíveis se baseia em ligações pendentes de silício (SiDB). Este trabalho visa comparar a robustez de uma coleção proposta de portas lógicas representadas em SiDB a variações em parâmetros físicos de interesse.

## I. INTRODUÇÃO

Ao longo das últimas décadas, a implementação de circuitos lógicos baseados em metal-óxido-condutor complementar (CMOS) passou por sucessivas crises. Até meados da década de 2000, em geral, melhorias na capacidade de processamento eram obtidas com sucessivos aumentos na frequência de operação dos dispositivos [1]. Porém, atingiu-se o chamado *power wall*, quando a dissipação de calor e consumo de energia dos processadores chegaram a um limite, que impediria que novos avanços ocorressem da mesma maneira sem que os custos de refrigeração e consumo de energia de novos chips se tornassem rapidamente proibitivos [2].

Naquele momento, a solução encontrada pela indústria foi apostar na paralelização, com um mesmo chip passando a possuir múltiplos núcleos de processamento. Os ganhos de poder computacional nas gerações de chips que sucederam tiveram um ritmo reduzido em relação ao estado anterior ao *power wall*, mas sustentaram avanços satisfatórios com respeito às demandas da indústria [2]. Porém, a capacidade de miniaturização dos chips chega a um limite enquanto as demandas por poder computacional se aceleram, sobretudo em aplicações como aprendizado de máquina e data centers de provedores de nuvem.

Dentro deste contexto, a busca por soluções que substituam ou complementem o CMOS se torna de importância ímpar. A nanocomputação por acoplamento de campo próximo (FCN) se mostra uma alternativa extremamente promissora, pela capacidade de miniaturização sem precedentes, baixíssimo consumo de energia e dissipação de calor. Em particular, a

implementação de FCN baseado em ligações pendentes de silício (SiDB) se mostra promissora, com a implementação da lógica representada a partir de um substrato de silício passivado com hidrogênio sendo uma das alternativas mais interessantes [3], sobretudo por sua capacidade de funcionar em temperaturas mais altas [4].

Neste trabalho, apresenta-se um conjunto sistemático de testes da resistência de portas lógicas implementadas em SiDBs sobre uma superfície passivada de silício a variações em parâmetros físicos chave para o seu correto funcionamento e uma discussão dos resultados encontrados. Foram propostas três perguntas principais de pesquisa. Uma visão geral da tecnologia, conceitos fundamentais e trabalhos relacionados são apresentados na seção II. A definição das perguntas de pesquisa, bem como uma descrição detalhada do experimento conduzido são providenciadas na seção III. Os resultados obtidos são discutidos na seção IV, enquanto conclusões e perspectivas para trabalhos futuros são discutidas na seção V.

## II. CONCEITOS FUNDAMENTAIS E TRABALHOS RELACIONADOS

### A. A Plataforma de SiDB

Na representação lógica em pontos quânticos de silício, ao contrário da representação em CMOS, não há corrente elétrica, mas apenas perturbações eletrônicas sucessivas que são propagadas. O substrato no qual a lógica é implementada é uma superfície de silício passivado com hidrogênio ( $H\text{-Si}(100)\text{-}2\times1$ ). Com um microscópio de tunelamento por varredura, é possível retirar, com precisão atômica, átomos de hidrogênio da superfície de modo a deixar algumas ligações pendentes [5]. Cada ligação pendente (DB) pode assumir três estados de carga (-1, 0 e +1), mas é conveniente usar DBs em pares com um elétron compartilhado por par, que atua como um ponto quântico. A posição relativa do elétron compartilhado pode ser perturbada por interação com um campo externo, podendo vir de DBs vizinhos. A partir desta plataforma, posicionando-se estrategicamente pares de DBs é possível propagar perturbações de modo a obter um comportamento lógico designado. DBs adicionais podem ser colocados

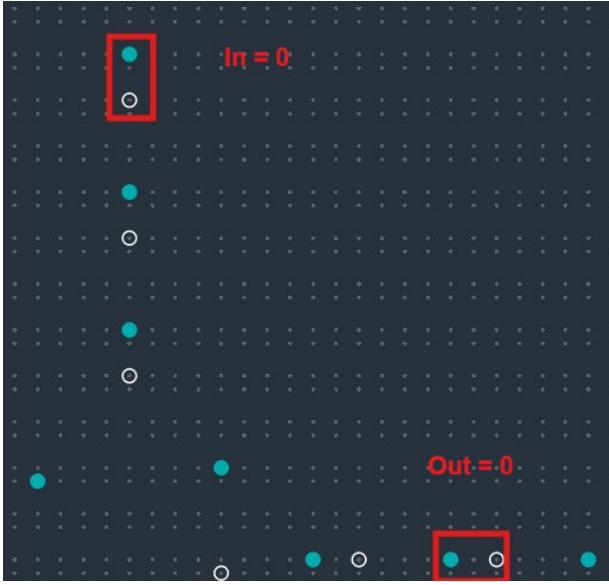

Fig. 1. Fio 1U1R, que propaga o sinal de entrada que vem de cima para a direita. Note o estado dos pares de DBs de entrada e saída, propagando o lógico (correspondente ao elétron orbitando o DB mais à esquerda em um par horizontal ou mais acima em um par vertical)

próximos à entrada e à saída com a função de alterar o estado do sistema, funcionando como perturbadores. Na fig. 1 há um exemplo de fio que propaga um sinal de entrada 0 vindo da direção de cima para a direita.

Nas interações entre os elétrons compartilhados por ligações pendentes, a configuração tende ao estado fundamental, de maior metaestabilidade. Conforme visto em [5], a estabilidade de uma configuração eletrônica em SiDBs depende de fontes externas de potencial eletrostático, do estado de carga de cada SiDB e do potencial de blindagem de Coulomb.

$$E(\vec{n}) = \sum_i V_i^{\text{ext}} n_i + \sum_{i < j} V_{ij} n_i n_j \quad (1)$$

O potencial de blindagem de Coulomb ( $V_{ij}$ ), por sua vez, depende da distância entre SiDBs ( $r_{ij}$ ), da permissividade relativa no vácuo ( $\epsilon_0$ ), da permissividade relativa do meio ( $\epsilon_r$ ) e do comprimento de blindagem de Thomas-Fermi ( $\lambda_{\text{TF}}$ ). Note que  $\epsilon$  na eq. 2 corresponde ao produto de  $\epsilon_0$  e  $\epsilon_r$ .

$$V_{ij} = \frac{q_0}{4\pi\epsilon r_{ij}} e^{-r_{ij}/\lambda_{\text{TF}}} \quad (2)$$

Por fim, há o potencial químico ( $\mu_-$ ), definido como a diferença entre o nível de Bulk de Fermi e o nível de transição de carga (0/-) de um DB.

### B. Figuras de Mérito

Dentre os parâmetros físicos que afetam a metaestabilidade de um sistema de SiDBs, três se destacam por serem variáveis com respeito à região da superfície em que se encontram. Tanto  $\epsilon_r$  quanto  $\lambda_{\text{TF}}$  são sensíveis a imperfeições na fabricação do material, além da distância relativa de átomos dopantes (de outros elementos que não o silício, inseridos para modular

propriedades eletrostáticas do material), enquanto  $\mu_-$  está fortemente ligado à concentração e distância relativa de átomos dopantes na estrutura [5]. Por mais que seja desejável obter uma superfície perfeitamente homogênea com respeito a estes três parâmetros, isto não é, em geral, realista.

Em [3], os autores propuseram um conjunto de figuras de mérito para circuitos baseados em SiDBs e uma métrica para tentar quantificar para mais de uma figura de mérito ao mesmo tempo. Neste trabalho, serão apenas investigadas as figuras de mérito do domínio operacional e da temperatura crítica. O domínio operacional de um circuito de SiDBs é definido como o conjunto de valores para  $\epsilon_r$  e  $\lambda_{\text{TF}}$  para os quais ele exibe o comportamento lógico esperado para todas as combinações de entradas. É desejável que uma configuração de SiDBs tenha uma área de domínio operacional tão amplo quanto possível. A temperatura crítica, por sua vez, é a maior temperatura para a qual o circuito ainda funciona corretamente. A diferença de energia entre estados de excitação na escala atômica é na ordem de meV, portanto, o ruído térmico pode afetar significativamente o estado do sistema. Acréscimos na temperatura eventualmente anulam a confiabilidade de circuitos de SiDBs. Portanto, é desejável que uma configuração tenha valores elevados de temperatura crítica.

### C. Trabalhos Relacionados

A análise sistemática do comportamento de layouts de portas lógicas no contexto de figuras de mérito de layouts de SiDBs, sobretudo do domínio operacional (OD) e da temperatura crítica (CT) já possui alguma bibliografia. No artigo seminal da simulação de circuitos baseados em SiDBs [1], os autores discutem extensivamente o conceito e medem os domínios operacionais de um conjunto de implementações propostas em forma de Y e de T para portas lógicas básicas. A temperatura crítica, por sua vez, foi investigada a partir da proposição de figuras de mérito críticas para o design de circuitos baseados em SiDBs [3]. Em particular, alguns dos designs de fios explorados no presente trabalho já tiveram medidos experimentalmente alguns dos aspectos explorados no presente trabalho - sobretudo seu domínio operacional e suas temperaturas críticas dentro de alguns valores predefinidos para  $\mu_-$  [4]. Além disso, outros autores já realizaram análises de domínio operacional [6] [1] para portas de outras bibliotecas propostas. Ainda, recentemente houve a publicação de um trabalho de Walter et al que explora as variações da temperatura crítica dentro do domínio operacional de alguns circuitos [7]. Este trabalho se diferencia por avaliar a variação da temperatura crítica dentro da área do domínio operacional com respeito a  $\epsilon_r$  e  $\lambda_{\text{TF}}$  junto do comportamento da temperatura crítica quando  $\epsilon_r$  e  $\lambda_{\text{TF}}$  são fixados e apenas  $\mu_-$  é variado. Por fim, as portas analisadas neste experimento não fazem parte das bibliotecas estudadas nos trabalhos preegressos, mas de uma biblioteca de autoria de J. G. O. Bicalho que deverá ser publicada futuramente.

### III. METODOLOGIA E EXPERIMENTO

#### A. SiDB One

Todos os circuitos lógicos do presente trabalho pertencem a uma classe proposta de biblioteca de portas para simulações de circuitos baseados em SiDBs. Esta biblioteca visa, em particular, implementar a lógica de autômatos de pontos quânticos (QCA) por meio de SiDBs, seguindo um formato retangular fixo para geração das portas por meio do QuickCell [8]. A ideia central é que, com um formato fixado para os componentes básicos, eles possam ser combinados de forma independente da sua orientação. Há, porém, uma diferença fundamental: Enquanto no QCA padrão a estrutura atômica é simétrica, no substrato de SiDBs ela é assimétrica, com distâncias mínimas entre pares de SiDBs vizinhos sendo ligeiramente maiores no eixo horizontal que no vertical [1]. Isto tem uma implicação fundamental no design da biblioteca: rotações horizontais e/ou verticais nem sempre conservam o comportamento lógico do componente rotacionado. Na verdade, em fios e inversores em forma de L ele é invertido, e em portas mais complexas o comportamento é menos previsível, mas algumas implementações foram sistematicamente selecionadas de modo a permitir que todas as portas possuam rotações factíveis.

#### B. Objetivos do Trabalho

Dentre as contribuições pretendidas para o estudo da biblioteca proposta, se destacam três investigações. 1) Se um dado fio, porta ou inversor funcionar para determinados valores de  $\epsilon_r$  e  $\lambda_{TF}$ , sua temperatura crítica será constante dentro desta região operacional? 2) Para diferentes implementações da mesma porta lógica, quais terão maior robustez a variações nos seus parâmetros físicos ( $\epsilon_r$ ,  $\lambda_{TF}$  e  $\mu_-$ )? 3) Com os valores experimentalmente ótimos de  $\epsilon_r$  e  $\lambda_{TF}$ , para qual conjunto de valores para  $\mu_-$  o circuito exibirá comportamento lógico correto e o que acontecerá com sua temperatura crítica dentro destes valores?

#### C. Processo Experimental

Para atingir os objetivos propostos, foi utilizado o framework Fiction [10] em todos os experimentos. Primeiro, para obter o conjunto completo de portas representantes de todas as classes de equivalências da biblioteca SiDB One, foi preciso inverter o layout de alguns circuitos retangulares, de modo a preencher lacunas de algumas rotações de portas lógicas. Após este passo, executaram-se sucessivas simulações para cada porta de modo a variar sistematicamente os valores de  $\epsilon_r$  e  $\lambda_{TF}$ , testando o comportamento operacional da porta com os valores da iteração enquanto  $\mu_-$  estava fixado em -0.32. Além do comportamento operacional (1 se correto, 0 em caso contrário) também foi medida a temperatura crítica para o circuito em cada simulação. Ao fim, obteve-se a área do domínio operacional do circuito, junto de informações detalhadas sobre a sua temperatura crítica. Por fim, num conjunto separado de simulações, para cada porta fixou-se o valor de  $\epsilon_r$  em 5.6 e o de  $\lambda_{TF}$  em 5.0nm enquanto  $\mu_-$  foi variado entre -0.40 e -0.20, com variação de 0.01 a cada

iteração. Além de verificar se há operacionalidade para aquele valor de  $\mu_-$ , foi, também, medida a temperatura crítica para o conjunto de parâmetros.

### IV. RESULTADOS E DISCUSSÃO

#### A. Temperatura Crítica e Domínio Operacional

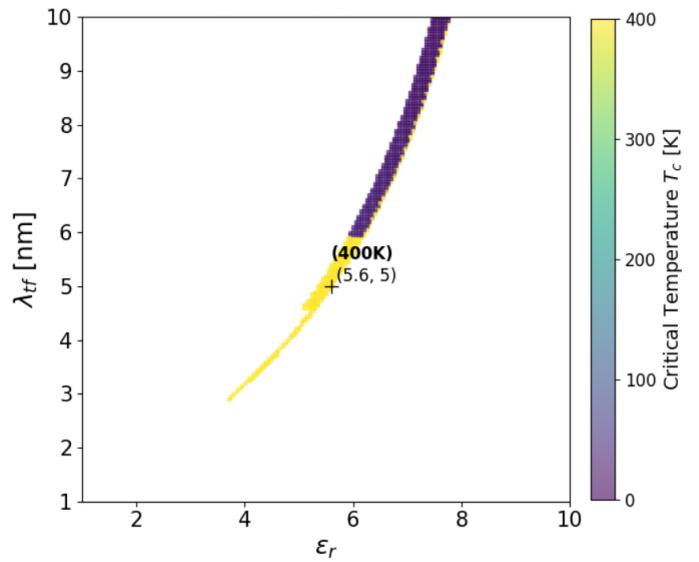

Na investigação sobre o que ocorre com a temperatura crítica dentro do domínio operacional de cada porta, os resultados obtidos mostraram um padrão consistente, com uma estrutura de temperatura crítica altamente volátil e descontínua. Como pode ser visto na fig. 2, não há um padrão intuitivo

Fig. 2. Mapa de calor do domínio operacional do NOR 2LU1R.

da interação entre a temperatura crítica e os valores de  $\epsilon_r$  e  $\lambda_{TF}$ , por vezes com temperaturas críticas mais altas sendo observadas em regiões de valores mais baixos, por vezes no extremo oposto. Em particular, é valiosa a percepção de que a temperatura crítica não necessariamente será maior nos valores otimais de  $\epsilon_r$  e  $\lambda_{TF}$ , destacados no gráfico. O padrão fortemente descontínuo observado no circuito destacado é semelhante ao observado nos demais circuitos testados. Os padrões são consistentes com os encontrados em [7].

#### B. Implementações de Classes Lógicas e Robustez

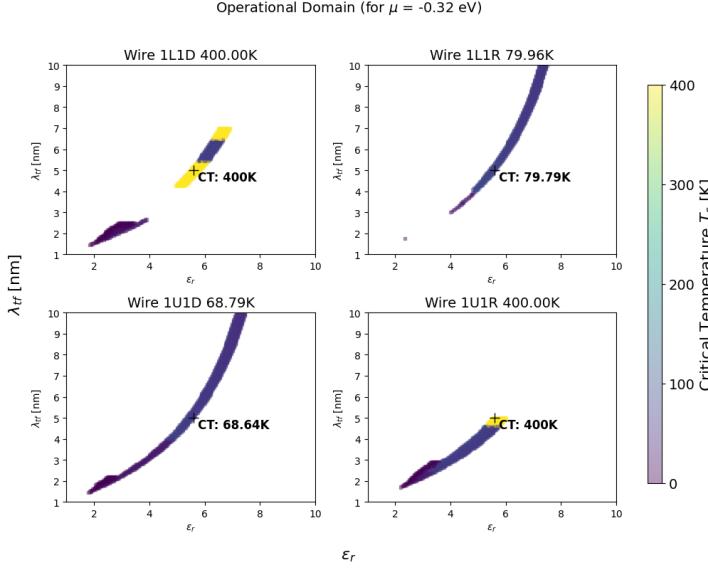

Outra questão de grande importância é observar quais versões de circuitos de mesmo comportamento lógico demonstram maior robustez às variações de parâmetros físicos, indicando o quanto viáveis são suas utilizações em componentes mais complexos. Por exemplo, pode-se preferir organizar os circuitos básicos de modo a favorecer que suas orientações mais estáveis e robustas ocorram com maior frequência. Na fig. 3 pode-se ver os perfis muito distintos tanto da área do domínio operacional quanto da temperatura crítica entre quatro implementações testadas de fios. Note que o domínio operacional do fio 1U1D tem uma área significativamente maior que a do fio 1L1D, mas seu comportamento térmico é menos desejável, com temperaturas críticas próximas de 0K.

Fig. 3. Mapas de calor dos domínios operacionais dos fios testados.

| Gate name  | Operational Domain Area Fraction |

|------------|----------------------------------|

| And 2Ld1R  | 0.0000                           |

| And 2Ld1U  | 0.0005                           |

| And 2Lu1D  | 0.0710                           |

| And 2Lu1R  | 0.0708                           |

| Inv 1L1D   | 0.0572                           |

| Inv 1L1R   | 0.0269                           |

| Inv 1U1D   | 0.0164                           |

| Inv 1U1R   | 0.0327                           |

| Nand 2Ld1R | 0.0194                           |

| Nand 2Ld1U | 0.0158                           |

| Nand 2Lu1D | 0.0095                           |

| Nand 2Lu1R | 0.0096                           |

| Nor 2Ld1R  | 0.0029                           |

| Nor 2Ld1U  | 0.0025                           |

| Nor 2Lu1D  | 0.0195                           |

| Nor 2Lu1R  | 0.0221                           |

| Or 2Ld1R   | 0.0209                           |

| Or 2Ld1U   | 0.0058                           |

| Or 2Lu1D   | 0.0257                           |

| Or 2Lu1R   | 0.0164                           |

| Wire 1L1D  | 0.0206                           |

| Wire 1L1R  | 0.0204                           |

| Wire 1U1D  | 0.0327                           |

| Wire 1U1R  | 0.0213                           |

| Xnor 2Ld1R | 0.0000                           |

| Xnor 2Ld1U | 0.0026                           |

| Xnor 2Lu1D | 0.0188                           |

| Xnor 2Lu1R | 0.0188                           |

| Xor 2Ld1R  | 0.0000                           |

| Xor 2Ld1U  | 0.0000                           |

| Xor 2Lu1D  | 0.0071                           |

| Xor 2Lu1R  | 0.0051                           |

Fig. 4. Proporção da região operacional sobre a região total investigada.

O padrão discrepante entre implementações se mantém nas demais classes testadas. Na fig.4 pode-se ver uma relação com as razões entre a área da região operacional de cada porta e a área total possível dos valores de  $\epsilon_r$  e  $\lambda_{TF}$ . Além das discrepâncias entre implementações, pode-se observar que algumas classes de portas têm muito mais fragilidade a imperfeições e oscilações no processo de fabricação que outras. Há, ainda, um padrão relacionado às portas que foram obtidas por meio de espelhamentos de outros circuitos, que será objeto de discussão adiante.

### C. A Relação entre $\mu_-$ , Viabilidade e Temperaturas Críticas

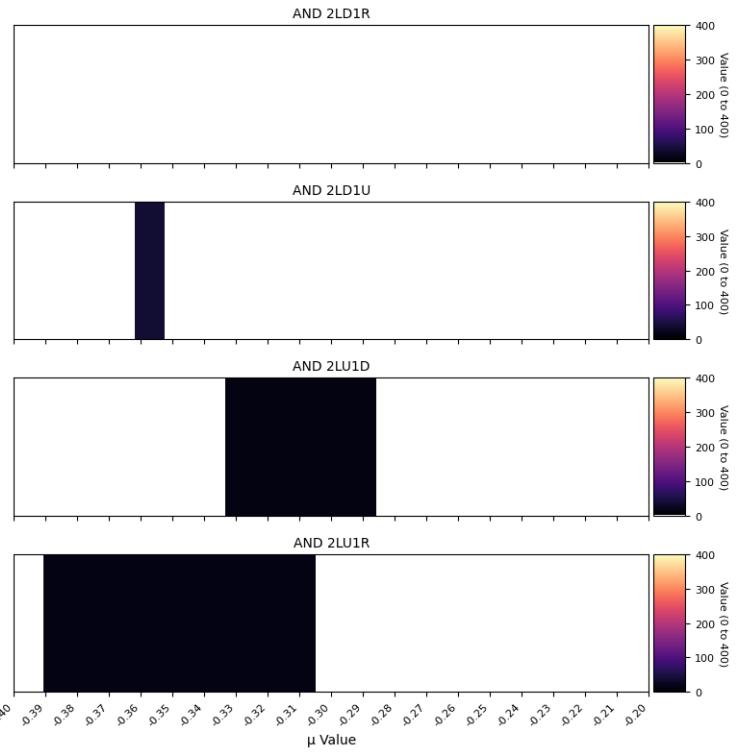

Por fim, o experimento que fixou os valores otimais para  $\epsilon_r$  e  $\lambda_{TF}$  enquanto variou somente  $\mu_-$  levou a resultados muito distintos dos anteriores. O que se observou de forma estável foram duas tendências principais: 1) As temperaturas críticas são aproximadamente constantes para todos os valores operacionais e; 2) Os valores viáveis de  $\mu_-$  são altamente previsíveis, tendo sido sempre contínuos e, com todas as exceções contidas nas portas obtidas por meio de espelhamentos de outros circuitos, incluem sempre o valor óptimo de -0.32. O primeiro padrão foi observado em todos os circuitos que foram operacionais para algum valor de  $\mu_-$ , o segundo para todos menos as portas NAND 2LD1R e AND 2LD1U, também obtidas por meio de inversões planares de outros layouts. Na fig.

Fig. 5. Regiões operacionais e temperaturas críticas de  $\mu_-$  para quatro portas AND testadas.

5 pode-se ver as regiões operacionais para quatro versões de portas AND testadas, que se diferem entre si pela geometria. As duas primeiras foram obtidas a partir de espelhamentos de outros circuitos. A previsibilidade da temperatura crítica, grande variação do alcance operacional e preferência pelo valor ótimo de -0.32 são tendências observadas nas demais classes de portas.

### V. CONSIDERAÇÕES FINAIS E TRABALHOS FUTUROS

Em todas as três questões de pesquisa avaliadas em ambas iterações experimentais, ficou claro que há alguns comportamentos anômalos nas portas que foram obtidas por meio de translações a partir de outros circuitos. É possível que as translações sejam imperfeitas e que, na verdade, circuitos

obtidos por meio de translações de outros circuitos não terão o mesmo comportamento em domínio operacional e temperatura crítica que o circuito original. Porém, é muito mais provável que tenham ocorrido erros humanos no passo de translação executado no início deste trabalho, sendo as anomalias resultados de perdas nestas translações. Com este pesar, talvez a comparação entre circuitos translados possa ser mais explorada em trabalhos futuros. Além disso, ainda não é claro o impacto de sistemas de clock sobre as translações [8], o que certamente será alvo de investigações na fronteira da pesquisa em FCN.

#### REFERENCES

- [1] S. S. H. Ng, J. Retallick, H. N. Chiu, R. Lupoiu, L. Livadaru, T. Huff, M. Rashidi, W. Vine, T. Dienel, R. A. Wolkow, and K. Walus, “Siqad: A design and simulation tool for atomic silicon quantum dot circuits”, IEEE Transactions on Nanotechnology, vol. 19, pp. 137–146, 2020.

- [2] D. A. Patterson, J. L. Hennessy, “Computer Organization and Design: The Hardware Software Interface RISC-V Edition”, Morgan Kaufmann Publisher, 2017.

- [3] J. Drewniok, M. Walter, S. S. Hang Ng, K. Walus and R. Wille, “Unifying Figures of Merit: A Versatile Cost Function for Silicon Dangling Bond Logic,” 2024 IEEE 24h International Conference on Nanotechnology (NANO), 2024, pp. 91-96

- [4] E. V. C. Ruella, J. G. O. Bicalho, R. S. Ferreira, O. P. V. Neto and J. A. M. Nacif, “A Comprehensive Analysis of Wire Performance in Silicon Dangling Bonds,” 2025 38th SBC/SBMicro/IEEE Symposium on Integrated Circuits and Systems Design (SBCCI), Manaus, Brazil, 2025, pp. 1-5

- [5] Jason Pitters, Jeremiah Croshaw, Roshan Achal, Lucian Livadaru, Samuel Ng, Robert Lupoiu, Taras Chutora, Taleana Huff, Konrad Walus, and Robert A. Wolkow ACS Nano 2024 18 (9), 6766-6816

- [6] M. D. Vieira et al., “Three-Input NPN Class Gate Library for Atomic Silicon Quantum Dots,” in IEEE Design & Test, vol. 39, no. 6, pp. 147-155, Dec. 2022

- [7] M. Walter, J. Drewniok and R. Wille, “The Operational Domain Explorer: A Comprehensive Framework to Unveil the Thermal Landscape of Silicon Dangling Bond Logic Beyond Conventional Operability,” 2025 IEEE 25th International Conference on Nanotechnology (NANO), Washington, DC, USA, 2025, pp. 28-33

- [8] J. Drewniok, M. Walter, S. S. H. Ng, K. Walus and R. Wille, “QuickCell: Fast Automatic Design of Standard Cells for Silicon Dangling Bond Logic,” in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems

- [9] J. G. O. Bicalho, private communication, November 2025.

- [10] M. Walter, R. Wille, F. S. Torres, D. Große, and R. Drechsler, “Fiction: An open source framework for the design of field-coupled nanocomputing circuits,” CoRR, vol. abs/1905.02477, 2019. [Online]. Available: <http://arxiv.org/abs/1905.02477>